# AN2752 Application note

# Getting started with STM8S and STM8AF microcontrollers

#### Introduction

This application note complements the information contained in STM8S and STM8AF datasheets by describing the minimum hardware and software environment required to build an application around these 8-bit microcontrollers.

This document also contains detailed reference design schematics with descriptions of the main components, and some hardware recommendations.

Some of the information given in Section 9: Software toolchain and Section 10: Setting up the development environment has a wider scope, to know if it applies to STM8 MCUs different from those of the STM8S and STM8AF Series contact your local representative.

April 2018 AN2752 Rev 6 1/40

# **Contents**

Contents

| 1 | Haro | Hardware requirements summary 6                               |            |  |  |  |

|---|------|---------------------------------------------------------------|------------|--|--|--|

| 2 | Pow  | er supply                                                     | 7          |  |  |  |

|   | 2.1  | Power supply overview                                         | 7          |  |  |  |

|   | 2.2  | Main operating voltages                                       | 8          |  |  |  |

|   | 2.3  | Power-on/power-down reset (POR/PDR)                           | 8          |  |  |  |

| 3 | Ana  | log-to-digital converter (ADC)                                | 0          |  |  |  |

|   | 3.1  | Analog power                                                  | 0          |  |  |  |

|   | 3.2  | Analog input                                                  | 0          |  |  |  |

| 4 | Cloc | ck management 1                                               | 2          |  |  |  |

|   | 4.1  | Clock management overview                                     | 2          |  |  |  |

|   | 4.2  | Internal clock 1                                              | 12         |  |  |  |

|   | 4.3  | External clock                                                | 2          |  |  |  |

| 5 | Res  | et control                                                    | 4          |  |  |  |

|   | 5.1  | Reset management overview                                     | 4          |  |  |  |

| 6 | Rece | ommendations                                                  | 6          |  |  |  |

|   | 6.1  | Printed circuit board                                         |            |  |  |  |

|   | 6.2  | Component position                                            | 6          |  |  |  |

|   | 6.3  | Ground and power supply (V <sub>SS</sub> , V <sub>DD</sub> )  | 6          |  |  |  |

|   | 6.4  | Decoupling                                                    | 16         |  |  |  |

|   | 6.5  | Other signals                                                 | 7          |  |  |  |

|   | 6.6  | Unused I/Os and features                                      | 7          |  |  |  |

|   | 6.7  | User options                                                  | 17         |  |  |  |

| 7 | Refe | erence design1                                                | 8          |  |  |  |

|   | 7.1  | Components reference                                          | 8          |  |  |  |

|   | 7.2  | Components reference         1           Schematics         1 | 9          |  |  |  |

| 8 | Deve | elopment tools                                                | <b>:</b> 0 |  |  |  |

|   |      |                                                               |            |  |  |  |

|    | 8.1   | Single wire interface module (SWIM)           | 20 |

|----|-------|-----------------------------------------------|----|

|    |       | 8.1.1 SWIM overview                           | 20 |

|    |       | 8.1.2 SWIM connector pins                     | 20 |

|    |       | 8.1.3 Hardware connection                     | 21 |

|    | 8.2   | Emulator STice                                | 21 |

|    |       | 8.2.1 STice overview                          | 21 |

|    |       | 8.2.2 STice in emulation configuration        | 22 |

|    |       | 8.2.3 In-circuit programming and debugging    | 23 |

| _  |       |                                               |    |

| 9  | Softv | vare toolchain                                |    |

|    | 9.1   | Integrated development environment            | 26 |

|    | 9.2   | Compiler                                      | 26 |

|    | 9.3   | Firmware library                              | 27 |

|    |       |                                               |    |

| 10 | Setti | ng up the development environment             | 28 |

|    | 10.1  | Installing the tools                          | 28 |

|    | 10.2  | Using the tools                               | 29 |

|    |       | 10.2.1 Project editing                        | 30 |

|    |       | 10.2.2 Online help                            | 31 |

|    | 10.3  | Running the demonstration software            | 32 |

|    |       | 10.3.1 Compiling the project                  | 32 |

|    |       | 10.3.2 Selecting the correct debug instrument | 33 |

|    |       | 10.3.3 Connecting the hardware                | 34 |

|    |       | 10.3.4 Starting the debug session             | 35 |

|    |       | 10.3.5 Running the software                   | 36 |

|    |       | 10.3.6 Follow up                              | 37 |

|    |       | umentation and on-line support                |    |

| 11 | Docu  | imentation and on-line support                | 38 |

| 12 | Povid | sion history                                  | 20 |

| 14 | Kevis | SIUII IIISIUI Y                               | J  |

تهيهوتوزيعقطعات الكترونيك

List of tables AN2752

# List of tables

| Table 1. | Component list            | 18 |

|----------|---------------------------|----|

| Table 2. | SWIM connector pins       | 20 |

| Table 3  | Document revision history | 39 |

AN2752 List of figures

# List of figures

| Figure 1.  | Power supply                                                                                   |    |

|------------|------------------------------------------------------------------------------------------------|----|

| Figure 2.  | External capacitor                                                                             |    |

| Figure 3.  | Typical layout of V <sub>DD</sub> /V <sub>SS</sub> and V <sub>CAP</sub> /V <sub>SS</sub> pairs |    |

| Figure 4.  | Analog input interface                                                                         |    |

| Figure 5.  | System clock distribution internal clock                                                       |    |

| Figure 6.  | Clock sources                                                                                  |    |

| Figure 7.  | Reset management                                                                               |    |

| Figure 8.  | Output characteristics                                                                         |    |

| Figure 9.  | Input characteristics                                                                          |    |

| Figure 10. | Reference design                                                                               | 19 |

| Figure 11. | Debug system block diagram                                                                     | 20 |

| Figure 12. | Hardware connection                                                                            | 21 |

| Figure 13. | Connection description                                                                         | 21 |

| Figure 14. | STice in emulation configuration                                                               | 23 |

| Figure 15. | In-circuit programming and debugging                                                           | 24 |

| Figure 16. | Software toolchain                                                                             |    |

| Figure 17. | Firmware library examples                                                                      |    |

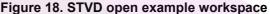

| Figure 18. | STVD open example workspace                                                                    | 29 |

| Figure 19. | STVD MCU edit mode                                                                             |    |

| Figure 20. | STM8 firmware library on-line help manual                                                      |    |

| Figure 21. | STVD: Building the project                                                                     |    |

| Figure 22. | STVD: Selecting the debug instrument                                                           |    |

| Figure 23. | Connecting the debug instrument to the STM8 evaluation board                                   |    |

| Figure 24. | STVD: Starting the debug session                                                               |    |

| Figure 25. | STVD: Running the software                                                                     |    |

| Figure 26. | STM8 evaluation board                                                                          | 37 |

**\**

AN2752 Rev 6 5/40

# 1 Hardware requirements summary

To build an application based on a microcontroller of the STM8S or STM8AF Series, the board must have at least the following features:

power supply

6/40

- · clock management

- reset management

- debugging tool support: single wire interface module (SWIM) connector.

AN2752 Power supply

### 2 Power supply

### 2.1 Power supply overview

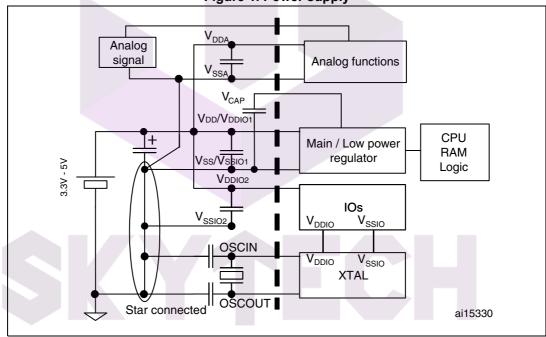

The device can be supplied through a 3.0~V to 5.5~V external source. An on-chip power management system provides the 1.8~V digital supply to the core logic, both in normal and low power modes. It is also capable of detecting voltage drops, on both external (3.3~V~/~5~V) and internal (1.8~V) supplies.

The device provides:

- one pair of pads  $V_{DD}/V_{SS}$  (3.3 V ± 0.3 V to 5 V ± 0.5 V) dedicated to the main regulator ballast transistor supply.

- two pairs of pads dedicated for  $V_{DD\_IO}/V_{SS\_IO}$  (3.3 V ± 0.3 V to 5 V ± 0.5 V), which are used to power only the I/O's. On 32-pin packages, only one pair is bonded.

Note: For  $V_{DDIO}/V_{SSIO}$  next to  $V_{DD}/V_{SS}$ , it is recommended to connect these two pairs together and to use only a decoupling capacitor. The purpose is to ensure good noise immunity by reducing the connection length between both supplies and also between  $V_{DD}/V_{DDIO}$  and the capacitor.

• One pair of pads  $V_{DDA}/V_{SSA}$  (3.3 V ± 0.3 V to 5 V ± 0.5 V) dedicated to analog functions. Refer to Section 3: Analog-to-digital converter (ADC) for more details.

Figure 1. Power supply

Note:

The capacitors must be connected as close as possible to the device supplies (especially  $V_{DD}$  in case of dedicated ground plane).

Placing a crystal/resonator on OSCIN/OSCOUT is optional. The resonator must be connected as close as possible to the OSCIN and OSCOUT pins. The loading capacitance ground must be connected as close as possible to  $V_{\rm SS}$ .

57

AN2752 Rev 6 7/40

Power supply AN2752

### 2.2 Main operating voltages

STM8S and STM8AF devices are made in 0.13  $\mu$ m technology. The STM8S and STM8AF core and I/O peripherals need different power supplies. In fact, STM8S and STM8AF devices have an internal regulator with a nominal target output of 1.8 V.

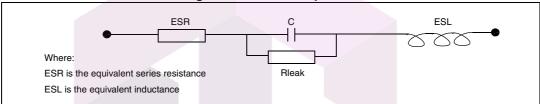

Stabilization for the main regulator is achieved by connecting an external capacitor  $C_{\text{EXT}}$  to the VCAP pin. Refer to the STM8S or STM8AF datasheets (available on *www.st.com*) for more information on the VCAP characteristics. Take care to limit the series inductance to less than 15 nH.

Figure 2. External capacitor

### 2.3 Power-on/power-down reset (POR/PDR)

The input supply to the main and low power regulators is monitored by a power-on/power-down reset circuit. The monitoring voltage range is 0.7 V to 2.7 V.

During power-on, the POR/PDR keeps the device under reset until the supply voltages ( $V_{DD}$  and  $V_{DDIO}$ ) reach their specified working area.

At power-on, a defined reset must be maintained below 0.7 V. The upper threshold for a reset release is defined in the electrical characteristics section of the product datasheet.

Hysteresis is implemented (POR > PDR) to ensure clean detection of voltage rise and fall.

The POR/PDR also generates a reset when the supply voltage drops below the V<sub>POR/PDR</sub> threshold (isolated and repetitive events).

AN2752 Power supply

#### Recommendations

All pins need to be properly connected to the power supplies. It is important to have the lowest possible impedance for these connections, including pads, tracks and vias. This is typically achieved with thick track widths and dedicated power supply planes in multi-layer printed circuit boards (PCBs).

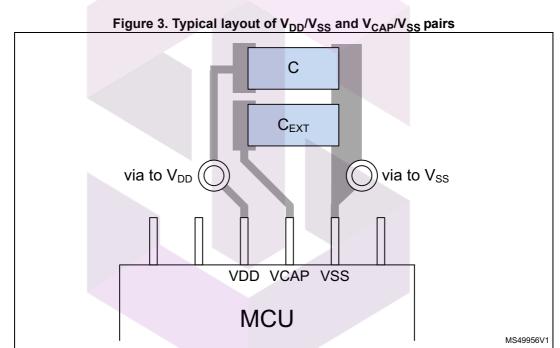

In addition, each power supply pair has to be decoupled with 100 nF filtering ceramic capacitors (C) with one chemical capacitor (1 to 2  $\mu\text{F})$  in parallel on the STM8S or STM8AF device. The ceramic capacitors (including  $C_{EXT}$  capacitor between VCAP and VSS pins) need to be placed as close as possible or below the appropriate pins, on the opposite side of the PCB. Typical values are 10 nF to 100 nF, but exact values depend on the application needs. Figure 3 shows the typical layout of the  $V_{DD}/V_{SS}$  and  $V_{CAP}/V_{SS}$  pairs.

AN2752 Rev 6 9/40

### 3 Analog-to-digital converter (ADC)

### 3.1 Analog power

The ADC has an independent, analog supply reference voltage, isolated on input pin  $V_{DDA}$ , which allows the ADC to be supplied by a very clean voltage source. This analog voltage supply range is the same as the digital voltage supply range on pin  $V_{DD}$ . An isolated analog supply ground connection on pin  $V_{SSA}$  provides further ADC supply isolation. Together, the analog supply voltage and analog supply ground connection, offer a separate external analog reference voltage input for the ADC unit on the  $V_{REF+}$  pin. This gives better accuracy on low voltage input as follows:

- V<sub>REF+</sub> (input, analog reference positive): the higher/positive reference voltage for the ADC needs to be between 250 mV and V<sub>DDA</sub>. For more details about V<sub>REF+</sub> values refer to the STM8S or STM8AF datasheets. This input is bonded to V<sub>DDA</sub> in devices that have no external V<sub>REF+</sub> pin (packages with 48 pins or less).

- V<sub>REF-</sub> (input, analog reference negative): the lower/negative reference voltage for the ADC has to be higher than V<sub>SSA</sub>. For more details about V<sub>REF-</sub> values refer to the STM8S or STM8AF datasheets. This input is bonded to V<sub>SSA</sub> in devices that have no external V<sub>REF-</sub> pin (packages with 48 pins or less).

### 3.2 Analog input

STM8S and STM8AF devices have 16 analog input channels, which are converted by the ADC one at a time, and each of them is multiplexed with an I/O.

The analog input interface of the ADC is shown in Figure 4.

Outside ADC

V<sub>IN</sub> | SW<sub>SAMP</sub>

V<sub>IN\_EXT</sub> | C<sub>SAMP</sub>

Figure 4. Analog input interface

#### Equation 1:

$$C_{VIN} = C_{SAMP} + C_{EXT}$$

#### where:

- C<sub>VIN</sub> is the total equivalent capacitor on the path of V<sub>IN</sub>

- C<sub>SAMP</sub> is the equivalent sampling capacitance

- C<sub>EXT</sub> is the total external capacitance on the path of V<sub>IN</sub> to the macro pin. This includes

parasitic routing capacitance, pad and pin capacitance and external capacitance. To

ensure proper and accurate sampling the following equation must be satisfied

#### **Equation 2:**

$$(R_{SW} + R_{EXT}) \times (C_{SAMP} + C_{EXT}) < \left(\frac{3}{10}\right) \times T_{S}$$

#### where:

- $R_{SW} = 30 \text{ k}\Omega$

- R<sub>EXT</sub> is the total external resistance on the path of V<sub>IN</sub>

- C<sub>SAMP</sub> = 3 pF

- $T_S = 0.5 \mu s$  (for 2 MHz input CLK)

Equation 2 is specific for R<sub>EXT</sub> and C<sub>EXT</sub> when designing an analog input interface for the ADC

Refer to the STM8S or STM8AF datasheets and/or to reference manual RM0016 (available on <a href="https://www.st.com">www.st.com</a>) for more details.

577

AN2752 Rev 6 11/40

Clock management AN2752

### 4 Clock management

### 4.1 Clock management overview

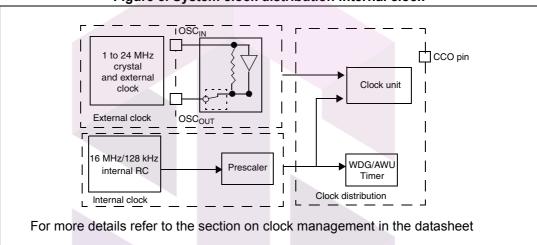

STM8S and STM8AF devices offer a flexible way of selecting the core and peripheral clocks (ADC, memory, digital peripherals). As shown in *Figure 5*, these devices have internal and external clock source inputs and one output clock (CCO).

Figure 5. System clock distribution internal clock

#### 4.2 Internal clock

The RC oscillator has an internal capacitor (C) and an internal resistor ladder (R). STM8S and STM8AF devices have two kinds of internal clock: a high speed internal clock (HSI) running at 16 MHz and a low speed internal clock (LSI) running at 128 kHz.

After reset, the CPU starts with the internal RC (HSI clock signal) divided by 8, i.e. 2 MHz.

#### 4.3 External clock

STM8S and STM8AF devices can connect to an external crystal or an external oscillator.

Note: When no external clock is used, OSCIN and OSCOUT can be used as general purpose I/Os.

Figure 6 describes the external clock connections.

تهيه وتوزيع قطعات الكترونيك

AN2752 Clock management

Hardware configuration STM8 OSCIN OSCOUT External clock (I/O available) External source Frequency: 32 kHz ... 24 MHz

Comparator hysteresis: 0.1 \* V<sub>DD</sub>

Caution: Without prescaler, a duty cycle of maximum 45/55% must be respected STM8 OSCOUT OSCIN Crystal/ceramic resonators Q1  $\mathsf{C}_{\mathsf{L2}}$ Load capacitors Frequency range: 1-24 MHz Wake-up time: < 2 ms @ 24 MHz Oscillation mode: Preferred fundamental Output duty cycle: Max 55/45% I/O's: Standard I/O pins multiplexed with  $\ensuremath{\mathsf{OSC}_{\mathsf{IN}}}$  and  $\ensuremath{\mathsf{OSC}_{\mathsf{OUT}}}$ Cload: 10 ... 20 pF Maximum crystal power: 100 μW

Figure 6. Clock sources

The values of the load capacitors  $C_{L1}$  and  $C_{L2}$  are heavily dependent on the crystal type and frequency. The user can refer to the datasheet of the crystal manufacturer to select the capacitances. For best oscillation stability  $C_{L1}$  and  $C_{L2}$  normally have the same value. Typical values are in the range from below 20 pF up to 40 pF ( $C_{load}$ : 10 to 20 pF). The parasitic capacitance of the board layout also needs to be considered and typically adds a few pF to the component values.

#### Recommendations

In the PCB layout all connections have to be as short as possible. Keep any additional signals, especially those that could interfere with the oscillator, locally separated from the PCB area around the oscillation circuit using suitable shielding.

AN2752 Rev 6 13/40

Reset control AN2752

### 5 Reset control

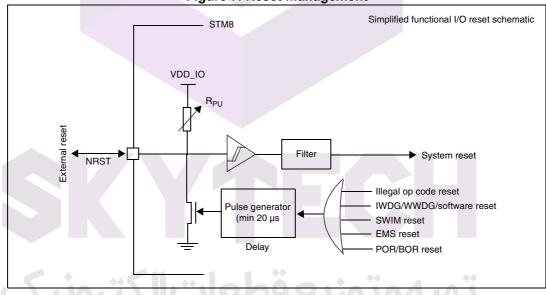

### 5.1 Reset management overview

The reset cell is a dedicated 5 V bidirectional I/O. Its output buffer driving capability is fixed to  $lo_{MIN}$  = 2 mA at 0.4 V in the 3 V to 5.5 V range, which includes a 40 k $\Omega$  pull-up. Output buffer is reduced to the n-channel MOSFET (NMOS). If a 40 k $\Omega$  pull-up is accepted, this cell does not include an output buffer of 5 V capability. The receiver includes a glitch filter, whereas the output buffer includes a 20 µs delay.

There are many reset sources, including:

- External reset through the NRST pin

- Power-on reset (POR) and brown-out reset (BOR): during power-on, the POR keeps

the device under reset until the supply voltage (V<sub>DD</sub> and V<sub>DDIO</sub>) reach the voltage level

at which the BOR starts to function.

- Independent watchdog reset (IWDG)

- Window watchdog reset (WWDG)

- Software reset: the application software can trigger reset

- SWIM reset: an external device connected to the SWIM interface can request the SWIM block to generate a microcontroller reset

- Illegal opcode reset: if a code to be executed does not correspond to any opcode or prebyte value, a reset is generated

- Electromagnetic susceptibility (EMS) reset: generated if critical registers are corrupted or badly loaded

Figure 7. Reset management

AN2752 Reset control

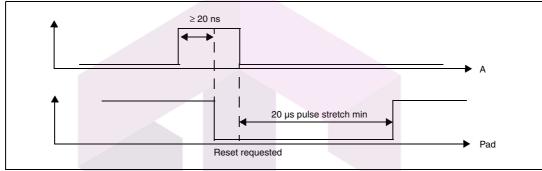

#### **Output characteristics**

• A valid pulse on the pin is guaranteed with a pulse whose duration is higher than 20 ns on the internal output buffer.

• After a valid pulse is recognized, a pulse of at least 20 μs is guaranteed on the pin, starting from the falling edge of A.

Figure 8. Output characteristics

#### Input characteristics

- All pulses with a duration lower than 75 ns are filtered

- All train/burst spikes with a ratio of 1/10 must be filtered. This means that a negative spike of up to 75 ns is always filtered, when a 7.5 ns interval between spikes occurs (ratio 1/10).

- All pulses with duration longer than 450 ns are recognized as valid

- After a valid pulse is recognized, an internal pulse of at least 30 ns is guaranteed

>7.5 ns >7.5 ns | 450 ns | 450 ns | 75 ns | 75

Figure 9. Input characteristics

AN2752 Rev 6 15/40

AN2752 Recommendations

#### 6 Recommendations

#### 6.1 Printed circuit board

For technical reasons, the best option is to use a multi-layer PCB with a separate layer dedicated to V<sub>SS</sub> and another layer to V<sub>DD</sub> supply, which results in a good decoupling, as well as a good shielding effect. For many applications, economical requirements forbid the use of this type of board. In this case, the most important feature is to ensure a good structure for the V<sub>SS</sub> and power supply.

#### 6.2 Component position

A preliminary layout of the PCB must separate the different circuits according to their electromagnetic interference (EMI) contribution in order to reduce cross-coupling on the PCB, i.e. noisy, high-current circuits, low voltage circuits, and digital components.

#### Ground and power supply (V<sub>SS</sub>, V<sub>DD</sub>) 6.3

The V<sub>SS</sub> has to be distributed individually to every block (noisy, low level sensitive, and digital) with a single point for gathering all ground returns. Loops must be avoided or have a minimum surface. The power supply needs to be close to the ground line to minimize the surface of the supply loop. This is due to the fact that the supply loop acts as an antenna, and is therefore the main emitter and receiver of EMI. All component-free surfaces of the PCB must be filled with additional grounding to create a kind of shield (especially when using single-layer PCBs).

#### 6.4 Decoupling

The standard decoupler for the external power is a 100 µF pool capacitor. Supplementary 100 nF capacitors must be placed as close as possible to the VSS/VDD pins to reduce the area of the current loop.

As a general rule, decoupling all sensitive or noisy signals improves electromagnetic compatibility (EMC) performance.

There are two types of decouplers:

- Capacitors close to components. Inductive characteristics, which apply to all capacitors beyond a certain frequency, must be taken into account. If possible, use parallel capacitors with decreasing values (0.1, 0.01, ... µF).

- Inductors. Although often ignored, ferrite beads, for example, are excellent inductors due to their good dissipation of EMI energy and there is no loss of DC voltage (which is not the case when simple resistors are used).

AN2752 Recommendations

### 6.5 Other signals

When designing an application, the following areas have an impact on the EMC performance:

- noisy signals (clock)

- sensitive signals (high impedance)

- signals for which a temporary disturbance permanently affects operation of the application, for example, interrupts and handshaking strobe signals (but not LED commands).

A surrounding  $V_{SS}$  trace for such signals improves EMC performance, as does a shorter length or absence of noisy and sensitive traces (crosstalk effect).

For digital signals, the best possible electrical margin must be reached for the two logical states. Slow Schmitt triggers are recommended to eliminate parasitic states.

#### 6.6 Unused I/Os and features

Microcontrollers are designed for a variety of applications, which fairly often do not use all the available microcontroller resources.

To increase EMC performance it is advisable to let free unused clocks, counters, or I/Os. As an example, set I/Os to '0' or '1' (pull-up or pull-down the unused I/O pins), and "freeze" or disable unused functions.

Alternatively, unused I/Os can be programmed as push-pull 'low' in order to keep them at a defined level, and not to use external components.

### 6.7 User options

STM8S and STM8AF devices have user option features that can be used for remapping or enabling/disabling an automatic reset or low speed watchdog. For more details refer to the product datasheet.

AN2752 Rev 6 17/40

Reference design AN2752

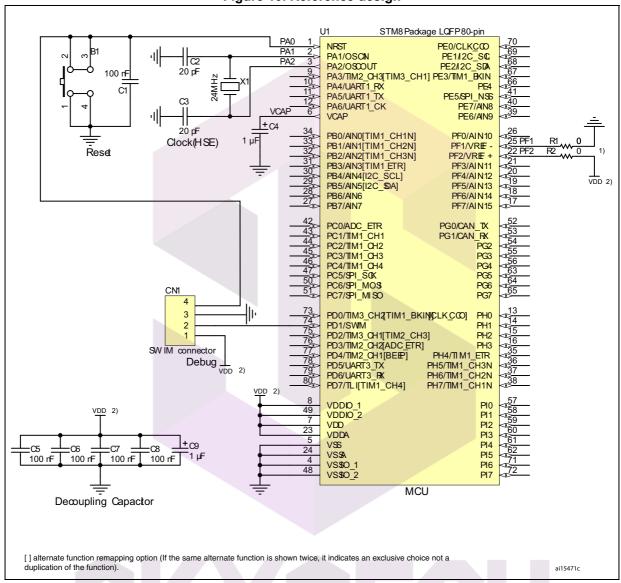

# 7 Reference design

### 7.1 Components reference

Table 1. Component list

| ID | Component       | Reference          | Quantity | Comments                                                                                                                        |

|----|-----------------|--------------------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| 1  | Microcontroller | STM8S or<br>STM8AF | 1        | Refer to the 'Pinouts and pin description' and 'Package characteristics' sections of the datasheets to choose the right package |

| 2  | Push button     | 1                  | 1        | -                                                                                                                               |

| 3  | Resistor        | 10 kΩ              | 1        | -                                                                                                                               |

| 4  | Capacitor       | 100 nF             | 5        | Ceramic capacitor (decoupling capacitor)                                                                                        |

| 5  | Capacitor       | 1 μF               | 1        | Decoupling capacitor                                                                                                            |

| 6  | Capacitor       | 1 μF               | 1        | Main regulator stabilization                                                                                                    |

| 7  | Capacitor       | 20 to 40 pF        | 2        | Used for crystal                                                                                                                |

| 8  | Crystal         | 1 to 24 MHz        | 1        |                                                                                                                                 |

| 9  | SWIM connector  | 4 pins             | 1        | -                                                                                                                               |

AN2752 Reference design

### 7.2 Schematics

Figure 10. Reference design

- 1. If pins 22 or 25 are required as GPIO, R1 and R2 has to be removed.

- 2. V<sub>DD</sub> must be within the allowed supply voltage range of the STM8S or STM8AF microcontroller.

AN2752 Rev 6 19/40

Development tools AN2752

### 8 Development tools

Development tools for STM8S and STM8AF microcontrollers include the STice emulation system supported by a complete software tool package including C compiler, assembler and integrated development environment with high-level language debugger.

### 8.1 Single wire interface module (SWIM)

#### 8.1.1 SWIM overview

In-circuit debugging mode or in-circuit programming mode are managed through a single wire hardware interface based on an open-drain line, featuring ultra fast memory programming. Coupled with an in-circuit debugging module, the SWIM also offers a non-intrusive read/write to RAM and peripherals. This makes the in-circuit debugger extremely powerful and close in performance to a full-featured emulator.

The SWIM pin can be used as a standard I/O (with 8 mA capability) which has some restrictions if the user wants to use it for debugging. The most secure way to use it is to provide a strap option on the PCB. Refer to the STM8 SWIM communication protocol and debug module user manual UM0470, available on <a href="https://www.st.com">www.st.com</a> for more SWIM protocol details.

DBG

Comm CMD decode

Internal RC

| SWIM entry Comm CMD decode | DM | STM8 core | RAM | NVM

Figure 11. Debug system block diagram

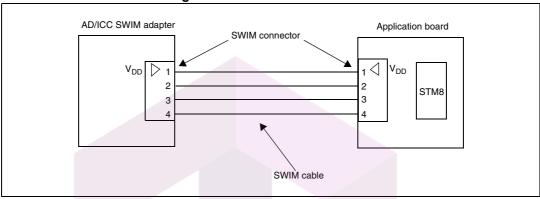

### 8.1.2 SWIM connector pins

The SWIM connector pins consist of four pins, as described in *Table 2*.

Pin number

Pin name

Pin 1

V<sub>DD</sub>

Pin 2

SWIM pin

Pin 3

V<sub>SS</sub>

Pin 4

Reset

Table 2. SWIM connector pins

AN2752 Development tools

#### 8.1.3 Hardware connection

Figure 12. Hardware connection

Caution:

It is recommended to place the SWIM header as close as possible to the STM8S or STM8AF device, as this minimizes any possible signal degradation caused by long PCB tracks.

### 8.2 Emulator STice

#### 8.2.1 STice overview

The STice is a modular, high-end emulator system that connects to the PC via a USB interface, and to the application board in place of the target microcontroller.

It is supported by the free STM8 toolset: IDE ST visual develop (STVD) programmer, ST visual programmer (STVP) and STM8 assembler. Refer to the STice emulator for STM8 for more details.

Emulation system

Connection flex

Connection adapter

Adapter socket

Figure 13. Connection description

577

AN2752 Rev 6 21/40

Development tools AN2752

#### **Emulation system: STice**

- Emulator box

- Cables for USB, power supply, trigger, analyzer input

#### **Connection flex**

• 60-pin or 120-pin cable for connection to the application board

#### **Connection adapter**

Links the connection flex to the footprint of the STM8S or STM8AF microcontroller

#### Adapter socket

Package-specific socket for connection adapter and STM8S or STM8AF microcontroller

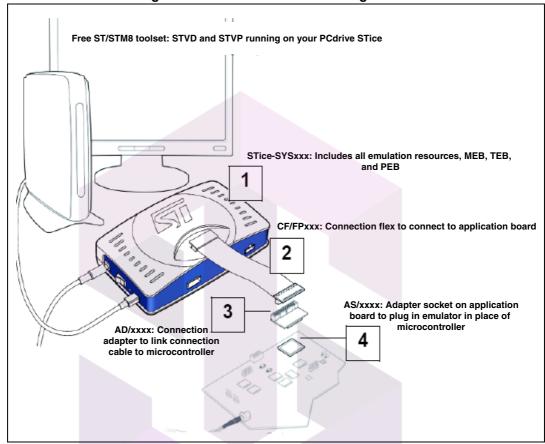

#### 8.2.2 STice in emulation configuration

In emulation configuration, the STice is connected to the PC via a USB interface and to the application board in place of the target microcontroller being used.

- Connection flex: Flexible cable (60-pin or 120-pin depending on the target microcontroller) that relays signals from the STice to the application board

- Connection adapter: Links the connection flex to the footprint of the target microcontroller on the users application board.

- Adapter socket: Socket that solders to the application board in place of the microcontroller and receives the connection adapter.

The above accessories are not included with the STice system. To determine exactly what is required for any supported microcontroller, refer to the online product selector on <a href="https://www.st.com">www.st.com</a>.

AN2752 Development tools

Figure 14. STice in emulation configuration

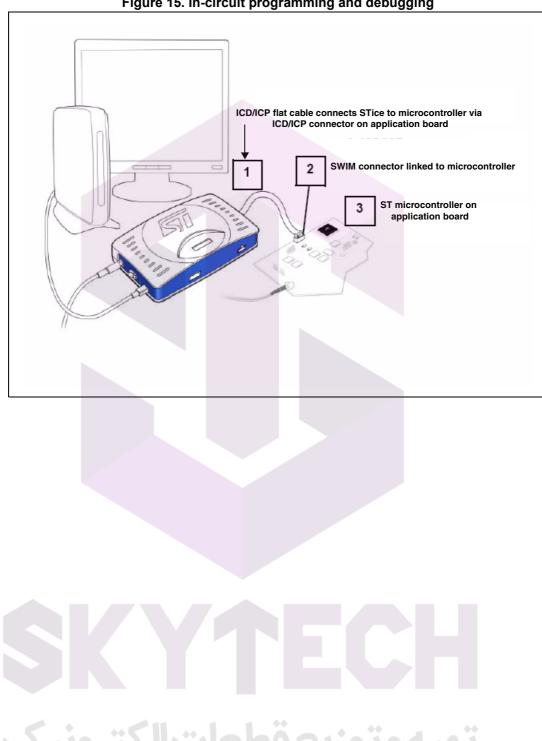

#### 8.2.3 In-circuit programming and debugging

In the in-circuit debugging/programming configuration, STice allows the application to be programmed in the microcontroller and for the application to be debugged while it runs on the microcontroller on the application board. STice supports the SWIM protocol, making it possible to in-circuit program and debug the microcontroller using only one general purpose I/O.

In both the emulation and the in-circuit programming/debugging configuration, STice is driven by the ST visual develop (STVD) or ST visual programmer (STVP) integrated development environment running on the host PC. This provides total control of advanced application building, debugging and programming features from a single easy-to-use interface.

577

AN2752 Rev 6 23/40

AN2752 **Development tools**

Figure 15. In-circuit programming and debugging

AN2752 Software toolchain

### 9 Software toolchain

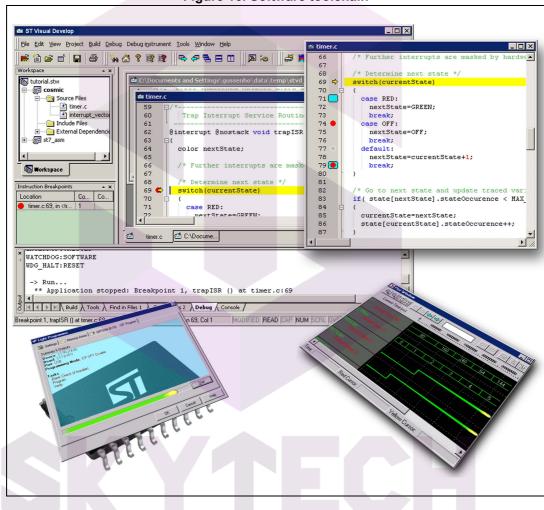

To write, compile and run the first software on an STM8S or STM8AF device, the following components of the software toolchain are required (see *Figure 16*):

- Integrated development environment

- Compiler

- Firmware library (optional, used to ease the start-up)

Figure 16. Software toolchain

AN2752 Rev 6 25/40

Software toolchain AN2752

### 9.1 Integrated development environment

The integrated development environment ST visual develop (STVD) provides an easy-to-use, efficient environment for start-to-finish control of application development, from building and debugging the application code to programming the microcontroller. STVD is delivered as part of the free ST toolset, which also includes the ST visual programmer (STVP) programming interface and the ST assembler linker.

To build applications, STVD provides seamless integration of C and assembly tool chains for ST including the Cosmic and Raisonance C compilers and the ST assembler linker. When debugging, STVD provides an integrated simulator (software) and supports a complete range of hardware tools including the low-cost RLink in-circuit debugger/programmer and the high-end STice emulator.

To upload applications to an STM8S or STM8AF device, the STVD also provides an interface for reading writing and verifying the microcontroller memories. This interface is based on the ST visual programmer (STVP), and supports all the target devices and programming tools supported by STVP.

The free ST toolset for STM8 is available on www.st.com.

### 9.2 Compiler

STM8S and STM8AF devices can be programmed by a free assembler toolchain which is included in the ST toolset.

As the core is designed for optimized high-level-language support, the use of a C compiler is strongly recommended.

C compilers for STM8 are offered by the third party companies Cosmic and Raisonance.

A free version of the C compiler with up to 16 Kbytes of generated code is available at www.cosmic-software.com and www.raisonance.com.

AN2752 Software toolchain

### 9.3 Firmware library

The firmware library is a complete set of source code examples for each peripheral. It is written in strict ANSI-C and it is fully MISRA C 2004 compliant (see *Figure 17*).

All examples are delivered with workspace and project definition files for STVD and Cosmic C compiler, which enables the user to load and compile them easily into the development environment.

The examples run on the STMicroelectronics STM8 evaluation board and can be tailored easily to other types of hardware.

For additional information on the STM8 firmware library, contact your nearest STMicroelectronics representative.

STM8S20x Firmware Library and Examples 📋 Usage 🖹 Known Bugs and Limitations 🖹 Peripheral drivers footprint Examples ADC Examples (2) 🐎 AWU Examples (1) 🐎 BEEP Examples (1) CLK Examples (4) EXTI Examples (1) FLASH Examples (4) GPIO Examples (2) 🔈 I2C Examples (5) > ITC Examples (1) 🃚 IWDG Examples (1) LINUART Examples (4) RST Examples (2) SPI Examples (3) TIMER1 Examples (5) 🐎 TIMER2 Examples (5) TIMER3 Examples (5) TIMER4 Examples (1) 🌭 USART Examples (9) WWDG Examples (1) Modules Data Structures Data Fields File List Directories Globals

Figure 17. Firmware library examples

AN2752 Rev 6 27/40

### 10 Setting up the development environment

The development environment for STM8S and STM8AF microcontroller setup looks different, depending upon the supplier of the software (SW) and upon the hardware (HW) tools.

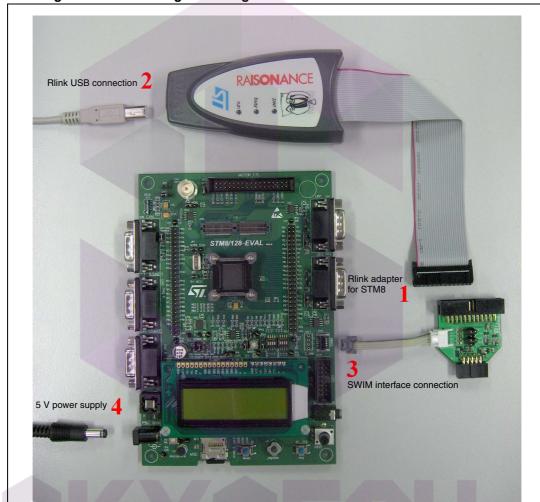

Typical setups are described below for the following SW and HW tools:

- STM8 C compiler from Cosmic

- ST toolset and STM8 firmware library from STMicroelectronics

- HW debug interface "Rlink" from Raisonance

- STM8 evaluation board from STMicroelectronics

### 10.1 Installing the tools

All software tools are delivered with a setup wizard that guides the user through the installation process. It is recommended to install the tools in the following order:

- C compiler

- 2. ST toolset

- 3. STM8 firmware library

Rlink does not need any dedicated software installation in the STM8 development environment because the necessary drivers are delivered with the ST toolset.

Note:

These R-link drivers must be launched separately as follows: Start/Programs/STtoolset/Setup/Install Rlink driver.

47/

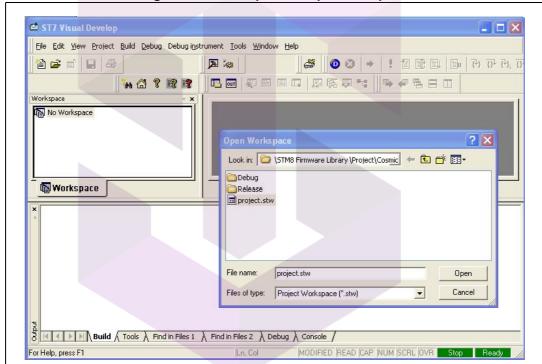

### 10.2 Using the tools

Once the tools installation is complete, the ST visual develop (STVD) integrated development environment can be launched.

The user then has the choice to generate either a new workspace with a new project or to open an existing workspace. When using the STVD for the first time, it is recommended to open an existing project from the STM8 firmware library.

The STM8 firmware library includes several examples for each peripheral plus a workspace containing a project which is already configured for the dot-matrix-display of the STM8 evaluation board. It is located in the firmware subdirectory \Project\Cosmic (see *Figure 18*).

AN2752 Rev 6 29/40

#### 10.2.1 Project editing

All project source files are visible and can be edited (see Figure 19).

Figure 19. STVD MCU edit mode

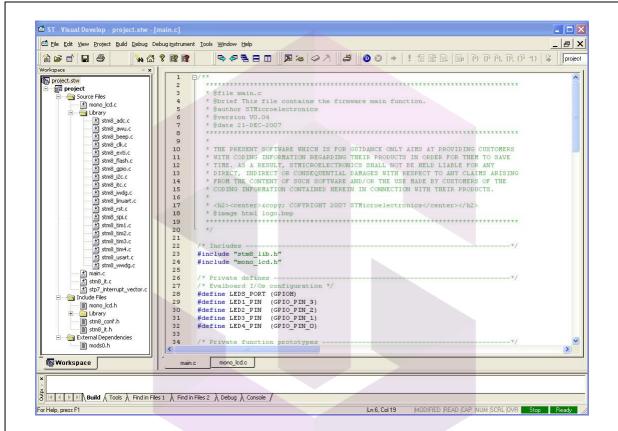

### 10.2.2 Online help

An online help manual is available inside the firmware installation directory (see *Figure 20*) to help the user understand the structure of the STM8 firmware library.

5//

Figure 20. STM8 firmware library on-line help manual

AN2752 Rev 6 31/40

### 10.3 Running the demonstration software

To run the demonstration software on the STM8 evaluation board, the project has to be compiled and the correct HW tool must be selected before the debug session can be started.

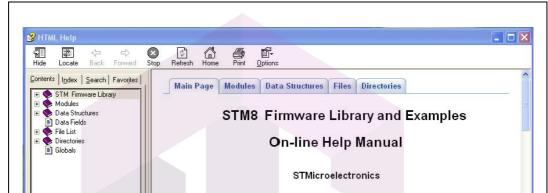

#### 10.3.1 Compiling the project

The project can be compiled using the Build function in the Build menu (see Figure 21).

Figure 21. STVD: Building the project

### 10.3.2 Selecting the correct debug instrument

In the example below, the Rlink tool is used for communicating via the SWIM interface with the on-board debug module of the STM8.

The Rlink tool can be selected from the Debug Instrument Selection list in the Debug Instrument Settings dialog (see *Figure 22*).

Figure 22. STVD: Selecting the debug instrument

AN2752 Rev 6 33/40

### 10.3.3 Connecting the hardware

The Rlink tool can be connected to the PC by a standard USB connection. It is also powered by the USB interface.

On the controller side the connection to the STM8 evaluation board is made by the SWIM interface cable. As shown in *Figure 23*, the board is powered by an external 5 V supply.

Figure 23. Connecting the debug instrument to the STM8 evaluation board

Caution:

On the Rlink ICC/SWIM adapter board, the "SWIM" jumper must be set. If there is no pull-up on the application SWIM line, the "ADAPT" jumper is also set. In any case, "PW-5V" and "12MHz" jumpers must not be set.

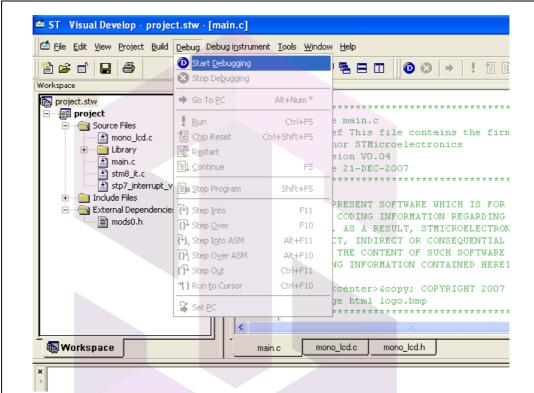

### 10.3.4 Starting the debug session

Debug mode can be entered by the command 'Debug Start Debugging' (see Figure 24).

Figure 24. STVD: Starting the debug session

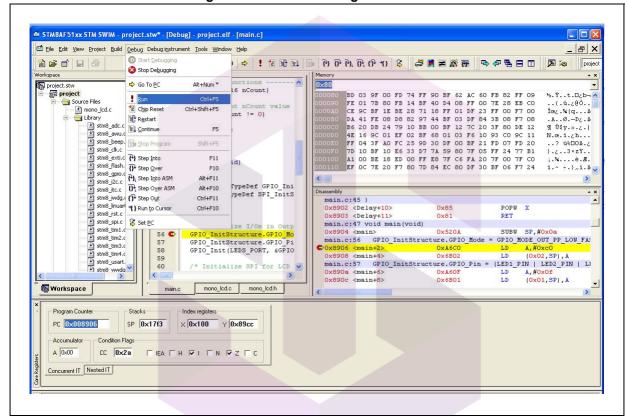

#### 10.3.5 Running the software

After entering debug mode, the software can be started by the run command in the menu 'Debug Run' (see *Figure 25*).

Figure 25. STVD: Running the software

The LCD display on the STM8 evaluation board indicates a successful debug session (see *Figure 26*).

Figure 26. STM8 evaluation board

### 10.3.6 Follow up

Step by step, additional peripherals of STM8S and STM8AFdevices can be run, following on from the initial debug session described above.

Many features of STM8S and STM8AFdevices are supported by dedicated hardware on the STM8 evaluation board. The necessary software drivers (CAN driver, LIN driver, buttons, memory cards, buzzer, etc) are delivered in the STM8 firmware library.

AN2752 Rev 6 37/40

#### 11 **Documentation and on-line support**

Documentation resources related to tool usage includes:

#### **Application**

- STM8S datasheets:

- STM8S207xx STM8S208xx

- STM8S105xx

- STM8S103K3 STM8S103F3 STM8S103F2

- STM8S903K3 STM8S903F3

- STM8S003K3 STM8S003F3

- STM8AFdatasheets:

- STM8AF52xx STM8AF6269/8x/Ax STM8AF51xx STM8AF6169/7x/8x/9x/Ax

- STM8AF622x/4x STM8AF6266/68 STM8AF612x/4x STM8AF6166/68

- How to program STM8S and STM8AF Flash program memory and data EEPROM (PM0051)

- STM8S and STM8AF microcontroller families reference manual (RM0016)

- STM8 CPU programming manual (PM0044)

#### **Tools**

- STM8 firmware library and release note (detailed descriptions of the library are included as help files)

- STice advanced emulation system for ST microcontrollers data briefing

- STice user manual

- Cosmic C compiler user manual

- STM8/128-EVAL evaluation board user manual (UM0482)

- ST visual develop tutorial (included as help files in the ST-toolchain)

- ST visual develop (STVD) user manual

- STM8 SWIM communication protocol and debug module user manual (UM0470)

The microcontroller discussion forum on www.st.com can be used by developers to exchange ideas. It is the best place to find different application ideas. In addition, the website has a knowledge base of FAQs for microcontrollers, which provide answers to many queries and solutions to many problems.

AN2752 Revision history

# 12 Revision history

**Table 3. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03-Jun-2008 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 01-Sep-2008 | 2        | STM8S207/208 replaced by STM8S20xxx  Figure 10: Reference design on page 19 and Figure 12: LQFP 80-pin pinout on page 21 modified to be in line with the pin description of the STM8S20xxx datasheet  Figure 7: Reset management on page 14 modified                                                                                                                                                                                                                                                          |

| 01-Apr-2009 | 3        | Modified Section 2.2: Main operating voltages on page 8                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 05-Aug-2011 | 4        | Table 1: General operating conditions: replaced Figure 10: Reference design on page 19: updated the value of the C4 capacitor.                                                                                                                                                                                                                                                                                                                                                                                |

| 31-Aug-2011 | 5        | Added STM8A throughout the document as this revision covers STM8A devices.  Replaced "Root part number 2" with STM8S and STM8A.  Updated Section 2.2: Main operating voltages: removed Table 1:  General operating conditions and added a reference to the STM8S and STM8A datasheets.  Removed Section 5.2: Hardware reset implantation.  Table 1: Component list: updated 'Reference' value for 'ID' 6.  Removed Section 7.3: Pinouts.  Updated references in Section 11: Documentation and on-line support |

| 04-Apr-2018 | 6        | Document scope limited to STM8S and STM8AF Series, hence updated title and <i>Introduction</i> .  Updated <i>Recommendations</i> and <i>Figure 3: Typical layout of VDD/VSS and VCAP/VSS pairs</i> .  Minor text edits across the whole document.                                                                                                                                                                                                                                                             |

AN2752 Rev 6 39/40

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved